Breaking Down the Semiconductor Value Chain, and How EDA Fits Within It

I recently listened to a podcast which piqued my interest in electronic design automation (EDA), a fascinating industry rife with innovation over the past forty years. It’s a great entree into the semiconductor industry as a whole, particularly because these software tools are inelastic to the companies that have been enthralled in the GenAI narrative (NVDA, AMD, and, by extension, MSFT, AMZN, META, GOOGL). In this article, I hope to frame EDA and its positioning relative to the foundries and chip designers in the broader semiconductor value chain.

What is EDA, and where does it fit within the broader semiconductor value chain?

EDA refers to software tools used by chip designers (Nvidia, AMD) to create the layout for their chip and verify its functionality before shipping it off to the foundries for manufacturing. The technology is built around logic synthesis, which converts a high-level description of a circuit's functionality into a gate-level representation that can be physically manufactured. The goal here is to ensure that the design meets specific requirements, such as area and power consumption. Timing analysis is another crucial aspect of EDA. After the logic has been synthesized into gates, timing analysis ensures that the circuit will operate correctly at the desired clock speed.

Let’s break that down a bit in the context of the value chain, starting with the manufacturing of the chips.

Equipment manufacturers like ASML use a leading-edge technology called extreme ultraviolet lithography (EUV) to harden a silicon wafer with incredibly precise patterns, which serve as the outlines for the process technology that will later be put in place by the foundry. In mastering this technology, ASML is literally pushing the laws of physics as we approach future process nodes at 2 nanometers. For context, each nanometer is roughly 5 atoms, so we’re talking about 10 atoms between each transistor. The systems themselves are simply used for projecting the patterns onto the silicon wafers and are sold to foundries at about $380 million a pop.

Once the foundry has received the machine, they need to make sure that the process technology allows for transistor sizes that keep up with the pace of technological development happening in the equipment space. In addition, TSMC needs to optimize its manufacturing to maximize the yield of functional chips from each wafer as quickly as possible. This is because so much of the cost of running a fab is tied up in the depreciation of capitally intensive equipment such that “filling the fab” is a priority akin to airlines’ priority to fill up empty seats; by failing to do so, you are essentially recognizing lost revenue on a depreciating asset (in this case, a plane). Because each node is so capitally intensive, the partnership established in 2014 between TSMC and Apple is crucial for TSMC. Whereas it took 8-9 quarters to reach 50% of peak node revenue run rate prior to 2014, TSMC now reaches that figure in just 2-3 quarters, shortening the payback period on massive amounts of capital investment required at each node. Take a breath, we’re done with manufacturing for now.

Then you have your chip designers, and these are the guys that are really making it happen. The chip design process (as I understand it) broadly consists of five steps, the first of which is high-level design and architecture. While this is the only step that is done solely by the chip designers, it is where the most creativity is allowed to happen. Take Nvidia for example: the reason their Compute Unified Device Architecture (CUDA) was such a masterstroke was because it allowed developers to write code that runs on Nvidia GPUs. Put another way, CUDA transformed the market for GPUs from traditional graphics, whose end markets were restricted largely to gaming, to broader parallel processing, allowing it to harness and become the focal point of the AI revolution. In AMD’s case, they introduced a “chiplet” architecture where, instead of designing a monolithic chip, they instead employed smaller, modular dies that are interconnected, improving manufacturing yields and allowing AMD to mix and match different cores. So yeah, a lot of innovation happens in step 1.

Step 2 of the process is where chip designers work on the design of the logic circuits, writing code in hardware description languages (HDLs) to integrate or even customize the Intellectual Property (IP) blocks (processor cores, memory controllers, etc). IP companies like Cadence, Synopsys, and ARM (the former two of which also participate in EDA) build libraries of pre-designed blocks of logic and circuitry which are used by chip designers to fulfill different functionalities depending on their design objectives.

Once the HDL is written, the EDA tools to perform what is called logic synthesis, where they take the high-level code specifying the chip’s functionality and convert it into the gate-level design that can actually be implemented on the silicon. Meanwhile, throughout this whole process, EDA tools must simultaneously understand what is possible at the foundry level from a physical manufacturing perspective.

Not to mention as the “A” would imply in EDA, all of this is automated! Yes, designers provide constraints like power consumption and timing, but the EDA can take those constraints and optimize the chip’s functionality in what is the third step of the process. And that’s created a bit of a flummox especially now that AI is being used for design space exploration — where AI algorithms analyze vast numbers of potential design configurations to identify the most optimal ones in terms of power, performance, and area — because the chip designer doesn’t even know what’s happening. A funny quote on that from Synopsys CEO Sassine Ghazi from the episode:

There was a lack of trust for about the first two years, even though the results were always better using the AI system, meaning the users could not trust it or use it because they wanted to answer the question, engineers. But I need to understand, what did it do? Of course, right now is a different story. AI is so well accepted that (the) question is gone.

After these three steps comes the easy but nerve-racking part: verification. EDA companies, but also simulation companies like Ansys (acquired by Synopsys, $ANSS), have tools that will verify not just the chip’s functionality, but the host of constraints that the designer may put forth on timing, power, size, etc.

Finally, we come back to the manufacturing players (equipment manufacturers and foundries) for the last step, commonly known as “tape-out.” When the final design is ready to be put through a fab, the designers will sign off on the verified chip functionality, while the EDA tools generate manufacturing files and ensure design compatibility with the foundry’s requirements. In fact, EDA companies automate the preparation of data that the foundry uses to create the photomasks that are used when fabricating the chips. Once the chips are fabricated, they are sent to assembly, test and packaging companies that continue to work the chip downstream until it finds its way into the device you’re reading this on, but that’ll be beyond the scope of this particular article.

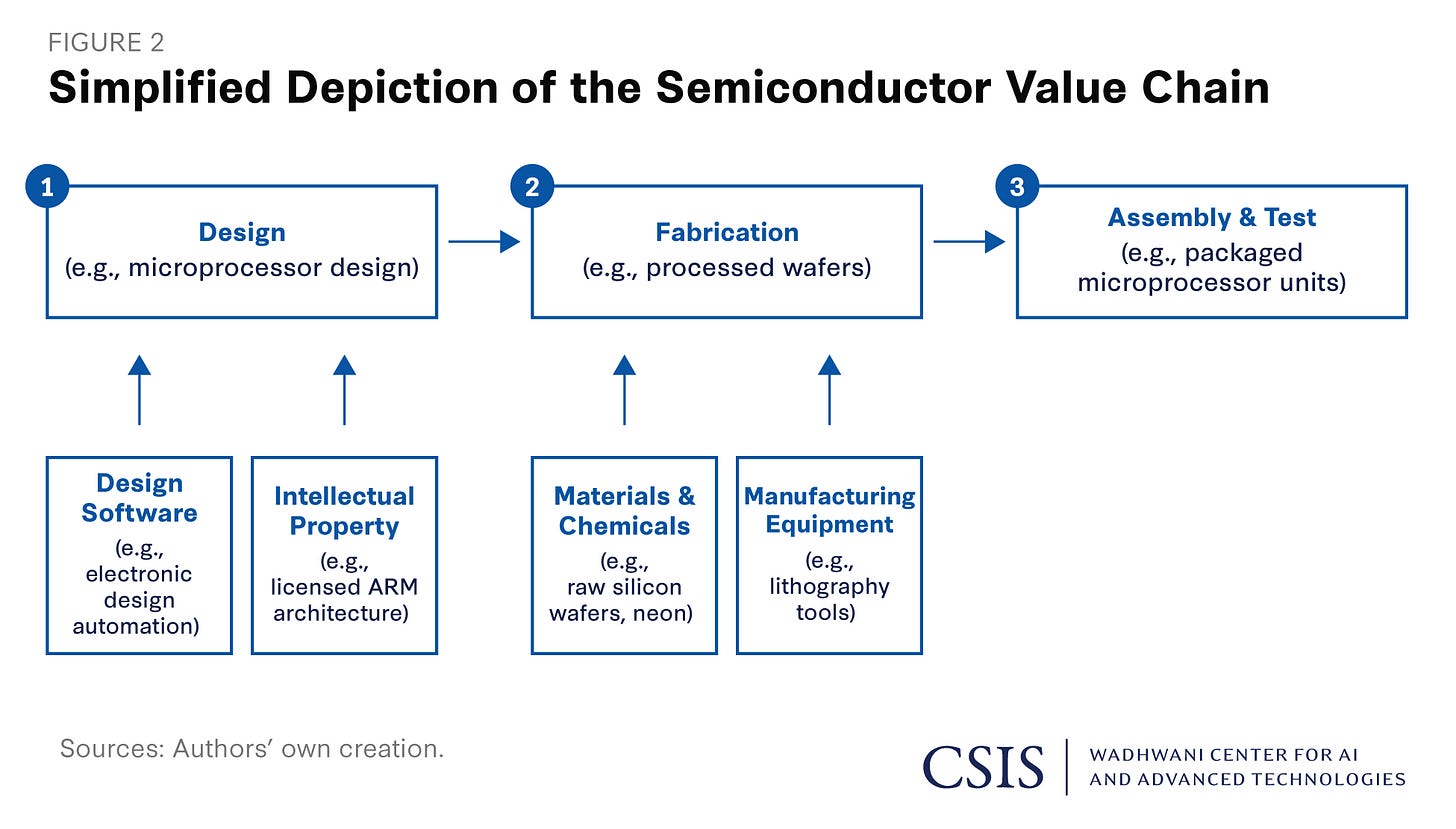

Here’s the thing I find utterly mind-blowing. At every process node, all of this technology needs to be in lockstep at the very least. Ideally, companies at any stage in the value chain are ahead of the other in terms of process technology. That way, an EDA company, for example, has up to date design software for when TSMC figures out how to reduce the number of atoms between two transistors, or when ARM’s IP library incorporates new architecture optimizations. See below for a value chain visualization from an article that greatly helped me understand this.

Glossary

Transistor: A tiny electronic device that acts like a switch or amplifier for electrical signals. Transistors are the basic building blocks of all modern electronic devices, including computers and smartphones. Invented by William Shockley at Bell Labs (spun out of AT&T) in 1947.

Block of Logic: A section of a chip that performs a specific function, like adding numbers or storing data. These blocks are made up of smaller components like transistors and are used to build the overall functionality of the chip.

Circuit: A complete path that allows electricity to flow, made up of components like transistors, resistors, and capacitors. In a chip, circuits are arranged to perform specific tasks, like processing data or controlling other devices.

Chiplet: A small piece of a larger chip that performs a specific function. Multiple chiplets can be combined to create a more powerful and versatile chip, allowing for more flexibility in design and manufacturing.

Process Technology: The method used to create the tiny components on a chip, like transistors. Process technology is often measured in nanometers (nm), with smaller numbers indicating more advanced technology that allows for more transistors to fit on a chip.

Monolithic Chip: A chip made from a single piece of silicon. This type of chip has all its components integrated onto one continuous piece of material, which can simplify design but may limit flexibility.

Modular Die: A type of chip design where different sections of the chip are created separately and then connected together. This allows for greater flexibility in design and can improve manufacturing efficiency.

Die: A small, flat piece of silicon that contains the actual circuits of a chip. After the circuits are created, the die is cut from a larger silicon wafer and packaged into a chip that can be used in electronic devices.

Manufacturing Yield: The percentage of good, working chips that come out of the manufacturing process compared to the total number produced. A higher yield means fewer defective chips, which is crucial for cost-effective production.

Timing Constraint (Placed by Chip Designer): A requirement set by chip designers that specifies how quickly signals must move through the circuit to ensure the chip works correctly. Meeting timing constraints is essential for the chip to operate at its intended speed.

Power Constraint (Placed by Chip Designer): A limit on how much electrical power a chip can use, set by the designers. Staying within this limit is important to prevent the chip from overheating and to ensure it operates efficiently.

Area Constraint (Placed by Chip Designer): A restriction on the physical size of the chip, determined by how much space the components can occupy. Designers must fit all necessary functions within this area while balancing performance, power, and cost.